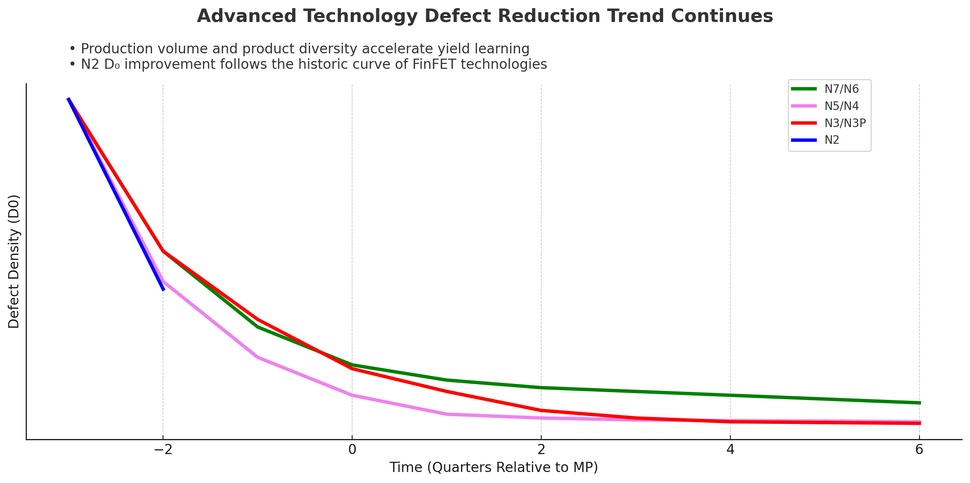

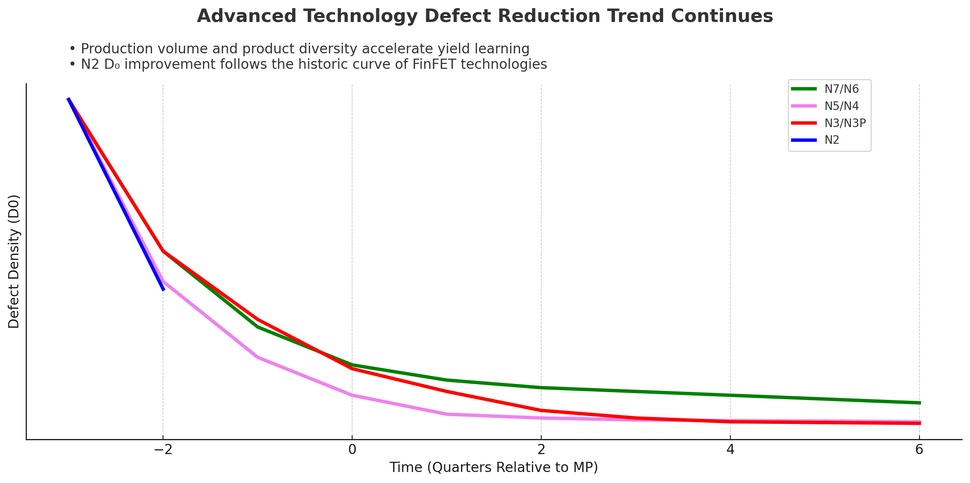

Нещодавно TSMC оголосив на семінарі з технологій Північної Америки про дефектну щільність (D0) технології процесів N2 (2NM) порівняно з його попередніми процесами на одній стадії.За даними компанії, щільність дефекту процесу N2 нижча, ніж у виробничих вузлах N3 (3 нм), N5 (5 нм) та N7 (7 нм).Крім того, слайд показує, що процес N2 TSMC все ще знаходиться в двох кварталах від масового виробництва, а це означає, що TSMC, як очікується, почне виробляти 2 нм мікросхем до кінця четвертої чверті 2025 року, як очікувалося.

Незважаючи на те, що процес N2 TSMC є першою технологією процесу компанії для прийняття наношетних транзисторів повного ворота (GAA), щільність дефекту цього вузла нижча, ніж процес попереднього покоління на тому ж етапі, на два квартали попереду масового виробництва (MP).Процеси попереднього покоління- N3/N3P, N5/N4 та N7/N6- всі використовувані транзистори зрілого плавника (FINFETS).Тому, хоча N2 є першим вузлом TSMC для прийняття транзисторів GAA Nanosheet, його зменшення щільності дефекту більше, ніж у процесі попереднього покоління перед входом у масове виробництво (HVM).

Ця діаграма зображує зміну щільності дефектів з часом, що триває з трьох кварталів до масового виробництва до шести кварталів після масового виробництва.Серед усіх відображених вузлів - N7/N6 (зелений), N5/N4 (фіолетовий), N3/N3P (червоний) та N2 (синій) - щільність дефектів значно зменшується зі збільшенням виходу, але швидкість зниження змінюється залежно від складності вузлів.Варто зазначити, що N5/N4 є найбільш активним у зменшенні ранніх дефектів, тоді як поліпшення врожаю N7/N6 відносно ніжне.Початковий рівень дефекту кривої N2 вищий, ніж у N5/N4, але потім різко зменшується, що дуже близьке до траєкторії зменшення дефектів N3/N3P.

Слайд підкреслює, що врожайність та різноманітність продуктів залишаються ключовими факторами рушійних факторів для прискорення поліпшення щільності дефектів.Більша продукція виробництва та диверсифікована продукція, що використовує один і той же процес, може швидше ідентифікувати та виправити проблеми з щільністю дефектів та врожайності, що дозволяє TSMC оптимізувати цикли навчання дефектів.TSMC заявив, що його технологія виробництва N2 отримала більше нових мікросхем, ніж його попередня технологія (оскільки TSMC тепер виробляє N2 мікросхеми для смартфонів та високопродуктивних обчислювальних клієнтів (HPC), що ризикують), і крива зниження дефекту в основному це відповідає.

Враховуючи фактори ризику, спричинені введенням нової архітектури транзистора, особливо важливо, щоб швидкість зменшення дефектів N2 залишалася узгодженою з попередніми вузлами на основі FINFET.Це вказує на те, що TSMC успішно передала свою експертизу навчання та управління дефектами до нової епохи Gaafet, не зустрічаючи значних невдач.

RFQs/замовлення (0)

RFQs/замовлення (0)

RFQs/замовлення (0)

RFQs/замовлення (0)